stratix 10 emif user guide

External Memory Interfaces Intel® Stratix® 10 FPGA IP User

The Intel Stratix 10 EMIF IP provides external memory interface support for DDR3, DDR4, Intel Stratix 10 General Purpose I/O User Guide.

Learn MoreEMIF DDR4 STRATIX 10 ,QUARTUS PRIME PRO 20.1 - Intel

2022. 1. 6. · Hi, I have Generated example design for emif stratix 10 and simulation scripts too. While simulating in the modelsim ,every signal has default values only. even calib_success&fail both were low only! one more thing ,I have generated emif core. With Avalon bus signal I am trying to feed some data,in this case aslo calibration is not going high.

Learn MoreIntel Stratix 10 SoC FPGA Boot User Guide

2021. 11. 10. · Updated for Intel® Quartus® Prime Design Suite: 21.4. This user guide describes the Intel® Stratix® 10 SoC FPGA boot flow, boot sources, and configuration bitstream generation.

Learn MoreIntel® Stratix® 10 Device Datasheet | Mouser

Direct Interface Bus (DIB) Intel Stratix 10 FPGA IP User Guide (75) In the SX device family, if the HPS EMIF is instantiated,

Learn MoreIntel Stratix 10 FPGA Developer Design Center Resources | Intel

2022. 8. 16. · Intel® Stratix® 10 FPGA Developer Center. The FPGA Developer Center is organized into industry-standard stages, which provides you with various resources to complete your Intel® FPGA design. Each design step is detailed in the expandable sub-sections with links that allow you to select and move between the various Generation 10 device series.

Learn MoreExternal Memory Interface Handbook Volume 2: Design

To enable the data pin inversion feature, click Configuration Register Settings > Option Control in the Arria 10 EMIF IP. QDR IV SRAM devices also have a

Learn MoreCentro de soporte de IP de interfaces de memoria externa - Intel

Video tutorial de estimación de especificaciones de EMIF. Herramientas de EMIF Intel Stratix 10 device pin-out y emiF address/command pin-out

Learn MoreStratix 10 EMIF Debug GUI - Intel Communities

Capabilities of the EMIF Debug GUI. The Stratix 10 On-Die Termination Tuning Tool helps find the optimal on die termination settings for an External Memory Interface or EMIF. This includes

Learn MoreStratix 10 External Memory Interface Simulation Guidelines Quartus

2022. 7. 31. · Generating the EMIF IP Double-clicking on Stratix 10 External Memory Interfaces opens the IP Parameter Editor 2. Provide a File Name for the EMIF IP 3. Click Create 6. Configuring the EMIF IP 4. Under Memory Protocol, select the appropriate Protocol from the drop-down list 5. Under the General tab, select the desired Speed Grade and Memory

Learn MoreHow to design a Memory interface with Intel FPGA

How to Implement External Memory Interface in Intel FPGA® Stratix 10 device. Brief introduction of the EMIF & design flow in Quartus Prime software.

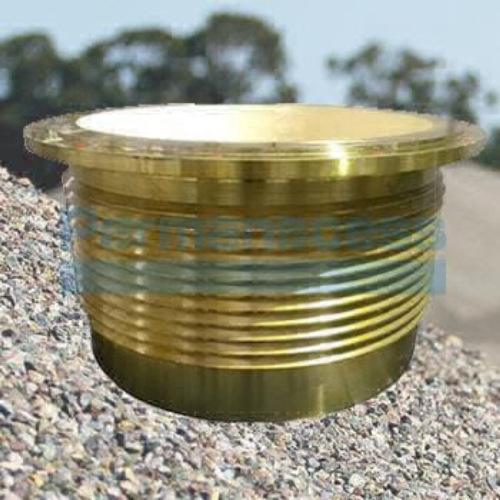

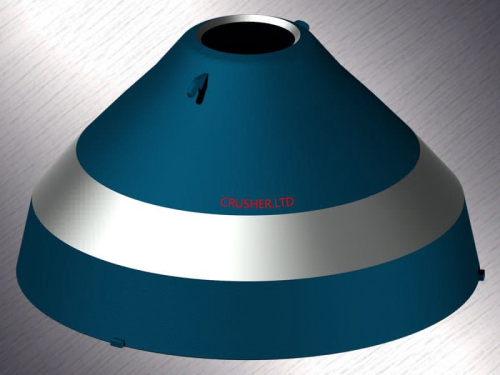

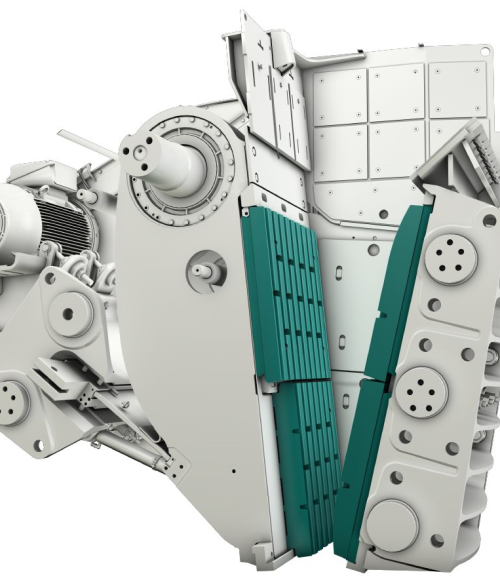

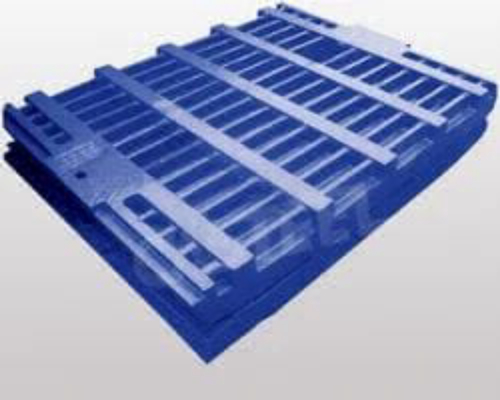

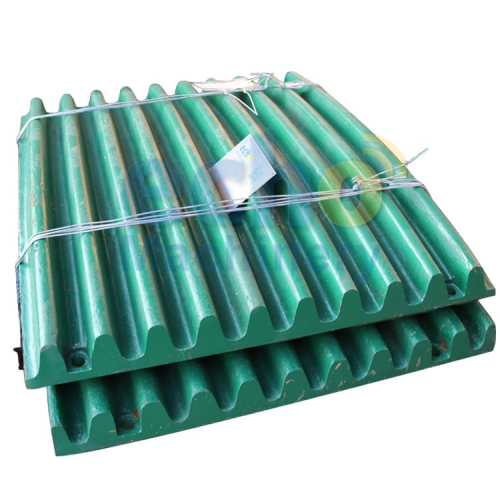

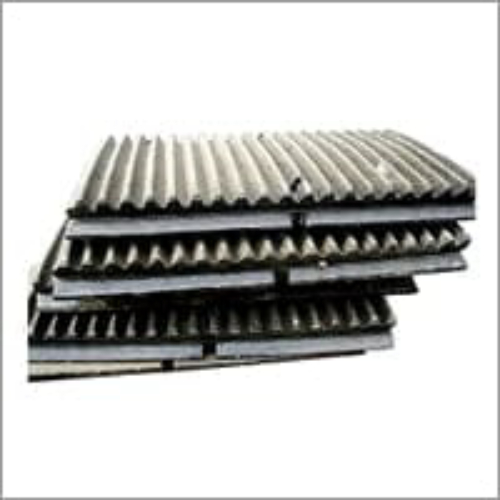

Learn MoreHP500 CNTRWGHT ASSY | stratix 10 emif user guide

Cone crusher main shaft Jaw crusher main shaft. Part of the rotary movement in the machine is mounted on the shaft. Usually the cone crusher or jaw crusher have a main shaft and a pinion shaft.

Learn More

Leave a comment